时钟分频电路设计和时钟分频器电路是电子系统设计中的重要组成部分,尤其在数字系统和嵌入式系统中,这些电路用于产生系统所需的不同频率的时钟信号,通常是从一个单一的较高频率源开始,通过分频得到所需的较低频率。

以下是关于时钟分频电路设计和时钟分频器电路的一些基本要点:

1、设计概述:

* 时钟分频电路的主要目标是从一个较高的频率源产生多个较低频率的时钟信号。

* 这些信号通常用于系统的不同部分,如CPU、存储器或其他数字组件。

2、分频器类型:

* 简单的分频器通常是二进制分频器,可以将频率减半。

* 更复杂的分频器可以产生多个不同的输出频率。

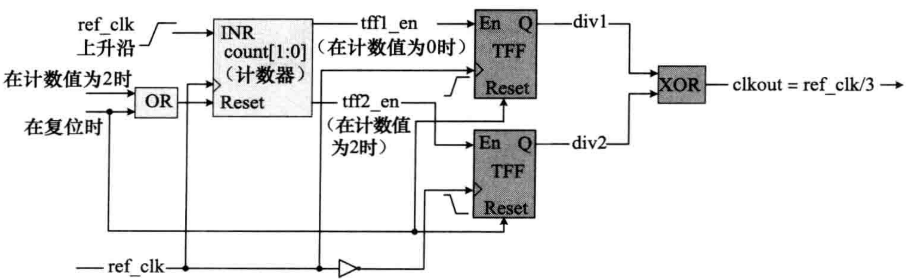

3、电路设计:

输入分频电路的输入通常来自一个稳定的时钟源,如晶体振荡器。

分频系数设计分频电路时,需要确定分频系数,即输入频率与输出频率的比值。

输出输出是所需的时钟信号,通常连接到系统的其他部分。

4、电路组件:

* 常用的组件包括计数器、寄存器和逻辑门。

* 计数器用于计算输入时钟的周期,并在达到预设的计数值时产生输出。

5、实际应用:

* 在嵌入式系统和微处理器中,时钟分频器用于产生各种总线时钟、处理器时钟和其他系统时钟。

* 在通信系统中,分频器用于产生适当的时钟信号以支持不同的通信协议。

6、注意事项:

稳定性确保分频电路能够产生稳定的输出频率。

抖动和噪声减小输出信号的抖动和噪声,以提高系统性能。

电源和功耗设计电路时需要考虑功耗和电源要求。

7、实例和参考设计:

* 可以参考现有的时钟分频器芯片或模块的设计文档和资料,以了解具体的实现方式和电路设计。

时钟分频电路设计和时钟分频器电路是电子系统设计中的重要部分,需要根据具体的应用需求和系统要求来设计和优化。

TIME

TIME